A Summary of Changes Between the Second and Third Revisions of the Nordic nRF51822/nRF51422 Chip

Tuesday, December 16, 2014

Objective: This document outlines the information you need for migrating from the 2nd to the 3rd revision of the nRF51822/51422 chip during development and/or production.

Quick Analysis: The additional features present in the new version of the chips are as follows:

- Increase in RAM

- Support for full Radio (TX/RX) and CPU concurrency

- Improved CPU Power efficiency

- Improved Start up time for Power on Reset

- More options with WLCSP packages

- 100% drop‐in and software compatible with Rev 2

- Bug Fixes

Detailed Analysis:

- Increase in RAM – On Rev 3 you can choose between 32 kB and 16 kB. On Rev 2, 16 kB was the maximum.

- Support for full Radio (RX/TX) and CPU concurrency –

- Support for running the CPU concurrently with the radio (RX and TX), both when encryption is enabled and not.

- On Rev 2, the CPU could run concurrently with the radio, however, not when encryption was being used.

- Key benefits include reduced application latency and increased CPU availability for application level code.

- New versions of the Soft Devices include APIs to enable/disable this feature.

- Improvement in Power efficiency –

- 300 uA reduction in active current for CPU executing code from flash. The CPU current, I_CPU, flash, is reduced with 300 uA, it is now 4.1 mA. On Rev 2, this current was 4.4 mA.

- Power Supply - Changed how the DC/DC and Regulators are organized. The new DC/DC converter only controls the radio voltage.

- Improved buck DC/DC regulator – Optimizations include automatic management (application software only needs to enable/disable the feature) and improved power efficiency.

- Improved the DC/DC solution – Simplified how the DC/DC is controlled and operates. Removed the complexity around how it is controlled. Removed the startup time issue.

- Improved start-up time for Power on Reset (POR) module in REV3 –

- Power on reset time (tPOR) is the time from when the supply starts rising to when the device comes out of reset and the CPU starts. The time increases with, and is inclusive of, supply rise time from 0 V to VDD.

- Optimized POR module to provide faster start-up time across the whole supply range (1.8 to 3.6 V).

- 100% drop‐in and software compatible with Rev 2

- Bug Fixes – Most of the bugs in the previous version are fixed in the newer version.

- 128kB flash wafer level chip scale package (WLCSP) – options for smaller wearable designs.

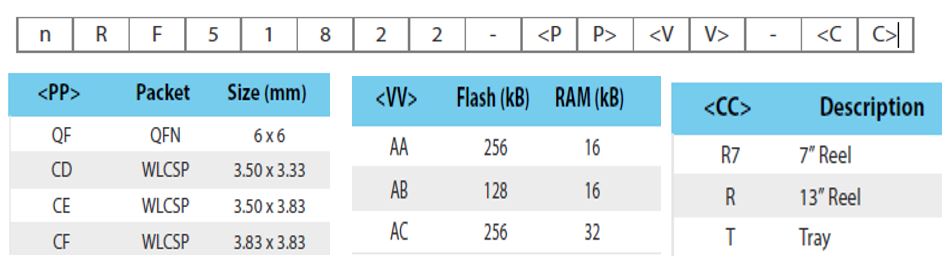

Package variants:

- QFN48 package, 6 x 6 mm

- WLCSP package, 3.50 x 3.83 mm

- WLCSP package, 3.83 x 3.83 mm

- WLCSP package, 3.50 x 3.33 mm

As compared to the earlier Rev, which was only available in

- QFN48 package, 6 x 6 mm

- WLCSP package, 3.50 x 3.83 mm

Concequences of Changes Introduced:

- Hardware – None. New revisions are drop-in compatible with the current revisions.

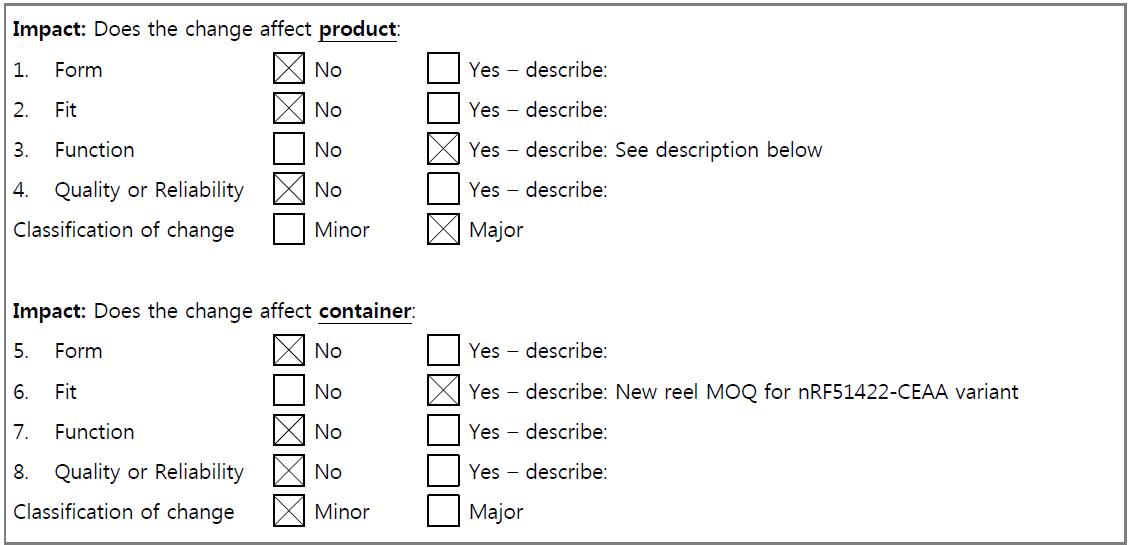

- Tele-regulatory and Bluetooth Certification – Reference designs nRF51822/51422-DF (QFN) and nRF51822/51422-CEAA-DF (CSP) pass all telecommunications regulatory bodies’ requirements with the stated product changes with no discernible performance change.

- Software – None. New revisions are software compatible with the current revisions including software workarounds for fixed anomalies.

Summary:

It is always recommended to use the latest versions of the hardware, SDK, and Soft Device. In addition to useful new features, most hardware and software updates bring with them bug fixes and improvements for optimal product performance.

Once you have taken into account the considerations covered in this document, the migration from an earlier version to one of the latest versions of the chip should be a relatively seamless process.

Nomenclature: